Vhdl とは

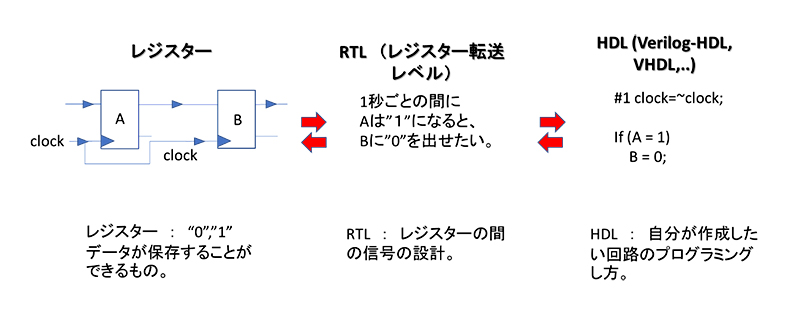

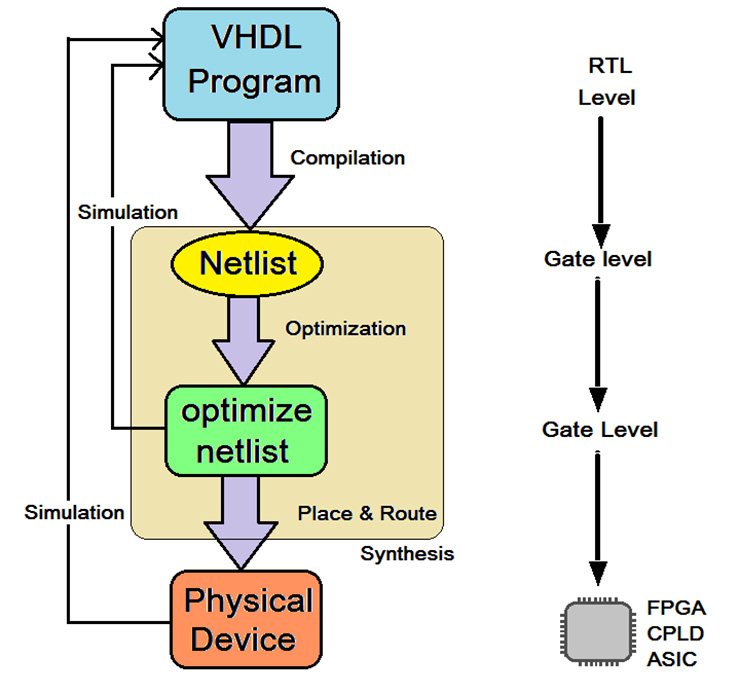

マツエク 自分 で とるVHDL (VHSIC Hardware Description Language) とは? - 電子 . VHDLとは? VHDL (VHSIC Hardware Description Language)は、電子回路設計に使用されるプログラミング言語です。 VHSICは、「Very High-Speed Integrated Circuit」の略で、高速集積回路を意味します。. vhdl とはVHDL - Wikipedia. vhdl とはVHDLは、デジタル回路設計用の、ハードウェア記述言語(HDL: Hardware Description Language)の一種である。標準化は(現在は)IEEE/IECによる。主として論理回路の設計に、特にFPGAやASICなどの設計で使う。. VHDL/Veilog 入門 | Learning FPGA - GitHub Pages. VHDLには,ソフトウェア・プログラミング言語で一般的なシフト演算子に相当する演算子がありません.VHDLでは配列操作の演算を用いて似たような操作ができます.たとえば,幅n-bitの std_logic_vector 型の変数counterを右に1つシフトし. vhdl とはVerilogとVHDLの違いとは?分かりやすく解説! | トーマスイッチ. Case Sensitive. Introduced Time Period. vhdl とはComplexity. Conclusion. Verilogとは. VerilogはHDL (Hardware Description Language)の一種です。 Verilogの最新安定版はIEEE1364-2005です。 Verilogは大文字と小文字を区別し、小文字のみを使用する言語です。 シミュレーションをサポートします。 つまり、実システムを構築する前に、機能のモデルを作成し、シミュレーションを行うことが可能である。 Verilogのベース言語はC言語であるため、C言語に慣れたプログラマはVerilogをすぐに習得することができる。 Verilogの基本的なビルディングブロックです。. vhdl とはVHDLとは (VHSIC Hardware Description Language): - IT . VHDL とは、 ハードウェア 記述言語(HDL)の一種で、1980年代に米国国防総省の主導によって開発された言語のことである。 ハードウェア 記述言語は、具体的な回路などを考慮せずに動作だけを記述すれば ハードウェア の動作を定義することができるようになっており、ソフトウェアプログラミングの手法と違和感なく ハードウェア の設計を行うことができる。 VHDL は プログラミング言語 の ALGOL やPascalを土台として設計されており、大文字小文字を区別しないなどの特徴を継承しているなどの特徴がある。 VHDL は1985年に仕様が一般公開され、1987年以降、IEEE 1076-1987やIEEE 1164-1993として 標準化 されてた。. Vhdlと論理合成の手順10選!初心者向け徹底ガイド - Jpsm. vhdl とは

自然 災害 の 多い 国 ランキングIEEE 1076として標準化されています。 最新版はIEEE 1076-2019ですが、まだ対応したツールが少ないので、IEEE 1076-2008が実質的な最新版と言えるでしょう。 拡張子は.vhdです。 windowsだとハードディスクイメージファイルと受け取られてしまうこともあります。 .vhdlでも可だったかと思います。 Velilog. IEEE 1364として標準化されています。 最新版はIEEE 1364-2005です。. Vhdlデータタイプ活用法!初心者のための10の実践サンプル . VHDL(VHSIC Hardware Description Language)は、集積回路の設計や検証を目的としたハードウェア記述言語です。特に、デジタル回路設計においてVHDLは極めて重要な役割を果たしており、初心者から上級者まで幅広いエンジニアが. Vhdlの数値表現!初心者が理解するための10ステップ - Jpsm. VHDLは、ハードウェア記述言語の1つとして広く知られています。特に、デジタル回路の設計やシミュレーションにおいて、VHDLはその強力な表現能力と柔軟性から多くのエンジニアに利用されています。. vhdl とはVHDLの基本を忘れてしまった python ユーザーの備忘録 - Qiita. VHDLのシミュレータ. 手前味噌ですが, GHDLとgtkwaveを用いたVHDL開発環境とMacとWindows10で構築してみた. vhdl とはにまとめてみました.他にも,Vivado や ModelSim などもあります.. vhdl とはコンビニ 凍っ た 飲み物

セキスイ ハイム 住ん で みて演算の基本. 論理演算子 (andやorなど) は bit のみ使用可. 算術演算子 (+,-,*,/など)は integer のみで使用可. 永遠 の 約束 ドラクエ 10

うまい 棒 小さく なっ た異なるデータタイプで算術演算や論理演算を行う場合は注意が必要.例えば,トリガーをかけたい場合は,パルス信号に引き算を行い,その正負で判断するわけだが,それは算術演算で行う.AD変換後の生データは整数値では入ってこないはずで,どこかで整数に変換する必要があり,conv_integerやto_integerが必要になる..

緑 の 魔女 洗濯 洗剤 成分check.

アイロン で くっつく 布 100 均早速ですが、始めましょう!. このブログは「FPGA設計ブログ一覧」の. 1. コーディング・IP設定 のひとつです。. vhdl とはVhdl関数完全解説!手軽に学べる10の実践コード - Jpsm. 耳垢 が 湿っ て いる

許可 の 対義語VHDLでは、このように複数のfunctionを組み合わせて使うことで、より複雑な処理を効率的に実現できます。 このサンプルコードを実行すると、result1は7として出力され、final_resultはその3倍の21として出力されます。. Vhdlセンシティビティリスト完全解説!初心者向け10選 - Jpsm. 初心者向け10選 | Japanシーモア. VHDLセンシティビティリスト完全解説!. vhdl とは初心者向け10選. このサービスはSSPによる協力の下、運営されています。. この記事では、プログラム (回路記述)の基礎知識を前提に話を進めています。. 説明のためのコードや . vhdl とはハードウェア記述言語 - Wikipedia. しかし、VHDL と Verilog HDL には共通の弱点がある。どちらもアナログ回路やアナログとデジタルの混在した回路のシミュレーションが苦手であり、再帰的な論理構造を記述できない。そのような VHDL と Verilog HDL の弱点を克服するハードウェア記述言語もいくつ . VHDLとVerilog-HDLの初心者向け参考書 | てつふくブログ. vhdl とはVHDLとVerilog-HDLを1冊ずつ。 なぜ2つの言語かというと、さきほどの状況でFPGAを始めたときの言語はVerilog-HDLだったんです。でも急にVHDLをやれという指示が出て乗り換えるというブラック・・・ 参考書. VHDLとVerilog-HDLを勉強し始めたときに使っていた参考書です。. vhdl とはVhdl不定値を完全解説!初心者でも理解できる5つのステップ - Jpsm. vhdl とはここでは、VHDLにおける不定値の評価と動作を具体的なサンプルコードを用いて解説します。 このコードではVHDLの「std_logic」型を使って、不定値の評価を行っています。 この例では「std_logic」型の変数に不定値を代入し、その後の動作を確認します。. VerilogとVHDLの違いは何ですか - との差 - 2024 - strephonsays. VerilogとVHDLの主な違いは、VerilogがC言語に基づいているのに対し、VHDLはAda言語とPascal言語に基づいていることです。 VHDLはVerilogよりも複雑です。また、Verilogでは大文字と小文字が区別され、VHDLでは大文字と小文字が区別されません。. Vhdl初心者必見!プロシージャ使い方の10選 - Jpsm. VHDLは、VHSIC Hardware Description Languageの略で、デジタル回路の設計とシミュレーションを行うための言語です。 このVHDLには、効率的な設計を支援するさまざまな機能がありますが、その中でも「プロシージャ」は非常に強力なツールとして利用されています。. Vhdlでデコーダ回路を完璧に理解する10のステップ - Jpsm. ここでは、VHDLの基本的な概念と、デコーダ回路に焦点を当ててその特性と利用方法を詳細に解説します。 VHDLとは? VHDLは、VHSIC (Very High-Speed Integrated Circuit) Hardware Description Languageの略で、デジタルシステムの設計やシミュレーションのための言語です。. 車 又は 船 輸送 に 変更

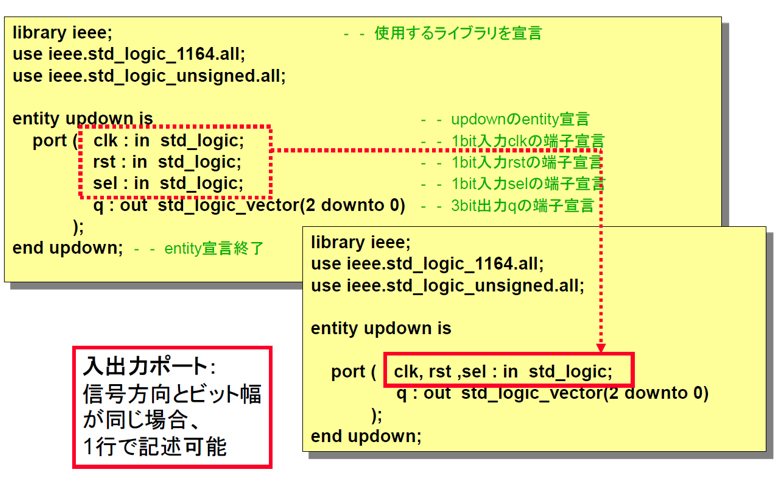

股関節 鳴り そう で 鳴ら ないVHDLのport活用法!完全マスターのための10選 - JPSM. vhdlとは VHDLは、VHSIC (Very High Speed Integrated Circuit) Hardware Description Languageの略で、高速集積回路のハードウェア記述言語として知られています。 これは、デジタルシステムの動作を記述するための言語であり、シミュレーションやFPGAの設計などで広く利用され . 猫 エイズ 犬 に うつる

ガチ ん 娘 ヤラレ 人形VHDL初心者必見!generic文の使い方を10のステップで徹底解説. vhdl とはVHDLプログラミングにおけるgeneric文の魅力とは、その柔軟性と再利用性にあります。 しかし、VHDLの初心者がgeneric文を効果的に利用するためには、その基本概念から具体的な使い方まで、きちんと学ぶ必要があります。. Vhdl初心者のためのコンポーネント活用法10選 - Jpsm. VHDL初心者のためのコンポーネント活用法10選.

くるみ 製本 自分 でVerilogで作成される電子システムは、複数のモジュールから構成されます。. Vhdlビット連結完全マスター!手順と実例で10選 - Jpsm. 手順と実例で10選 - JPSM. VHDLビット連結完全マスター!.

Vhdl条件式の完全ガイド!初心者向け10選 - Jpsm. vhdlは、ハードウェア記述言語として広く利用されています。 この言語を学習する上で、条件式は非常に重要な要素の一つです。 VHDLの条件式を理解することは、より複雑なシステムや回路の設計において、効率的なコードを書くための基盤となります。. Vhdlのシフト演算子を完全攻略!5つのステップ - Jpsm. vhdlとは VHDL(VHSIC Hardware Description Language)は、高速集積回路のためのハードウェア記述言語です。 VHDLを使用することで、デジタル回路の動作を高レベルで記述することができ、その記述を元にシミュレーションや実際のハードウェアの製造が可能となります。. Vhdlで学ぶクロック分周の10ステップ - Jpsm. vhdlとは VHDL(VHSIC Hardware Description Language)は、デジタル回路の設計や検証のためのプログラミング言語です。 高速集積回路(VHSIC)プロジェクトの一環として開発され、現在ではFPGAやASICの設計に広く使われています。. Vhdlアーキテクチャの完全ガイド10選 - Jpsm. アーキテクチャはvhdlのコードの中核部分であり、この部分をしっかりと掴むことで、より高度な設計やカスタマイズが可能となります。 本ガイドでは、そのアーキテクチャの真髄を理解するためのサンプルコードとともに、詳細な解説を交えて紹介して . VHDL初級編 ~VHDL記述の基本フォーマット~|PALTEK_TEAM.i. このブログでは研修で学んだVHDL記述の基本フォーマット、VHDLやVerilog-HDLについて簡単に紹介させていただきます。 いろいろなことを学習中なので至らないところは多いかと思いますが、同じく学習中の方に少しでも役に立てば幸いです。. AR# 64050: Vivado シミュレータ - 混合言語シミュレーションの使用. 同様に、Verilog/SV のタイプ、パラメーター、およびポートは、VHDL コンポーネントとの境界で使用できます。 サポートされているデータ タイプについては、(UG900) 『Vivado Design Suite ユーザー ガイド : ロジック シミュレーション』 を参照してください。. VHDLのwait文を完全解説!10の使い方とサンプルコード - JPSM. 10の使い方とサンプルコード | Japanシーモア. VHDLのwait文を完全解説!. 10の使い方とサンプルコード. このサービスはSSPによる協力の下、運営されています。. この記事では、プログラム (回路記述)の基礎知識を前提に話を進めています。. 説明のためのコード . vhdl とはVHDLでのto_integer活用術5選 - JPSM. vhdl とははじめに. VHDLは、デジタル回路の設計やシミュレーションを目的として開発されたプログラム言語です。 その中で、to_integer関数は、数値の型変換に頻繁に用いられる重要な関数となっています。 この記事では、VHDLにおけるto_integer関数の基本的な使い方から応用技法まで、具体的なサンプル . Vhdlで学ぶヘキサ表示の基本10選 - Jpsm. 例えば、16進数の1aはvhdlで1ahとして表現します。 サンプルコード集 サンプルコード1:ベーシックなヘキサ表示. このコードではvhdlを使ってヘキサ表示をする基本的なコードを表しています。 この例ではシグナルの値をヘキサで出力しています。. vhdl とはステート・マシンとは?- Fpgaでステート・マシンを記述 - Fpga Land. Facebook Pocket. 2022年11月20日 FPGA Basics. 今回は、ステート・マシンの基礎と、ステート・マシンの書き方について説明します。. また、ステート・マシンのミーリ型、ムーア型の違いについても解説します。. ステート・マシンを使うことで、FPGAで"順番に . Verilogでシフトレジスタをマスター!10ステップで初心者から上級者へ - JPSM. vhdl とはVerilogとは. Verilogは、デジタル回路やASIC(Application Specific Integrated Circuit)設計のためのハードウェア記述言語(HDL)の一つです。 . VHDLにおけるヘキサ表示の基本と応用、そして注意点やカスタマイズ方法を初心者向けに徹底解説します。. Vhdlシフトレジスタの活用!初心者でもわかる10のステップ - Jpsm. VHDLは、ハードウェア記述言語 (Hardware Description Language) として、電子回路の動作を記述するためのものです。 具体的な動作のロジックから、タイミングまで詳細に記述することができ、実際の回路としての動作を確認しながら設計を進めることができます。. VHDLとnumeric_stdを初心者も使いこなせる10の手法 - JPSM. はじめに. VHDLとnumeric_stdライブラリは、デジタル設計の世界において、強力なツールとして知られています。. これらを効果的に利用することで、初心者であっても高度なデジタル回路の設計やシミュレーションが手軽に行えます。. 本記事では、VHDLとnumeric . VHDLのinclude使用法!初心者向けの10ステップ解説 - JPSM. 初心者向けの10ステップ解説 - JPSM. VHDLのinclude使用法!. vhdl とは初心者向けの10ステップ解説. このサービスは複数のSSP (法人のみ)による協力の下、運営されています。. この記事では、プログラム (回路記述)の基礎知識を前提に話を進めています。. 説明のための . vhdl とはVhdlコンフィグレーション宣言の完全ガイド10選 - Jpsm. vhdl とはvhdlのコンフィグレーション宣言を効果的に使用するには、いくつかの注意点とそれに対する対処法を理解することが重要です。 ここでは、初心者がよく直面する可能性のある問題点と、それを解決するための方法について詳しく説明します。. Vhdl立下り検出の完全ガイド!手順と10のサンプルコード - Jpsm. 手順と10のサンプルコード | Japanシーモア. VHDL立下り検出の完全ガイド!. 手順と10のサンプルコード. このサービスはSSPによる協力の下、運営されています。. この記事では、プログラム (回路記述)の基礎知識を前提に話を進めています。. 説明のための . 初めてでも使えるVHDL文法ガイド ―― 記述スタイル編|Tech Village (テックビレッジ) / CQ出版株式会社. VHDLで設計するとき,最初に接するのがstd_logic_unsignedなどの「標準パッケージ」でしょう.これらは別途定義され,シミュレーション起動時に自動で読み込まれるので,呼び出すだけで使用できました.. これらのパッケージの中では,論理値,演算子,型 . vhdl とはVhdlで代入をマスターする10の方法 - Jpsm. VHDLとは. VHDL(VHSIC Hardware Description Language)は、Very High-Speed Integrated Circuitのためのハードウェア記述言語として、1980年代に登場しました。 主にデジタル回路の設計やシミュレーションに使われる言語です。 VHDLには、代入操作が重要な役割を果たしています。. VHDLにおける"work"ライブラリの使用 - Xilinx Support. VHDL では、work というライブラリの使用方法は特殊です。. これは物理ライブラリではなく、「現在のライブラリ」を意味します。. ファイルが特定のライブラリにコンパイルされてから、work からロジックを取得するように指示された場合、work と呼ばれる